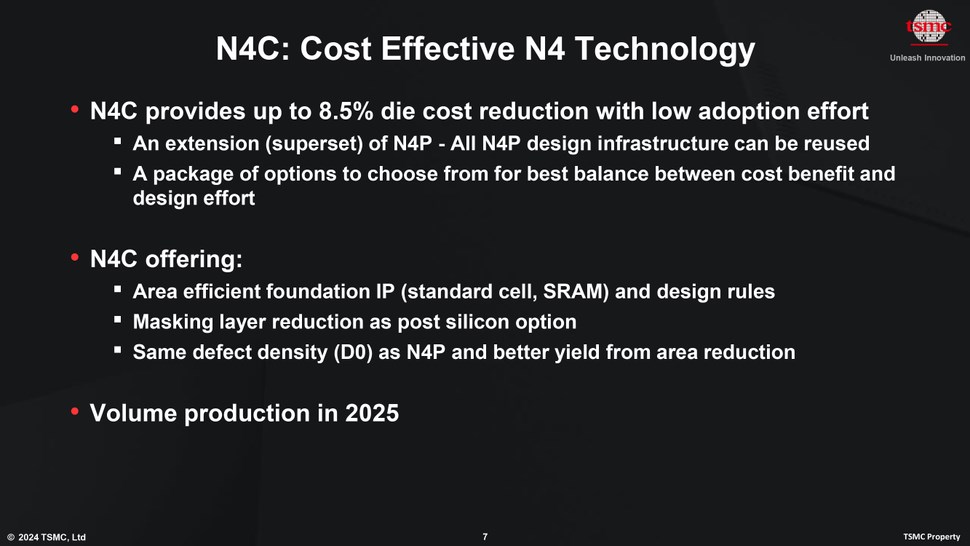

Maliyetleri %8,5 azaltacak

Mevcut N4P sürecinin optimize edilmiş ve maliyeti düşürülmüş sürümü olan N4C, daha uygun maliyetli ve verimli çiplerin önünü açacak. TSMC, standart hücreyi ve SRAM hücresini yeniden tasarlayarak, bazı tasarım kurallarını değiştirerek ve kullanılan maskeleme katmanlarının sayısını azaltarak maliyetleri %8,5'e kadar azaltmayı planlıyor. Böylece üretim süreci daha basit hale geliyor. Aynı zamanda zar alanı küçülerek daha az karmaşık ve verimli çiplerin önü açılıyor. TSMC, bu gelişmeler ile düşük maliyet arayan müşteriler için cazip bir seçenek sunmayı hedefliyor.

TSMC, N4C teknolojisini kullanan çiplerin üretimine 2025 yılında başlamayı planlıyor. 5nm sınıfı üretim sürecinde 6 yıllık bir deneyime sahip şirketin artık iyice rafine hale getirdiği teknolojisiyle önümüzdeki dönemde özellikle mobil alanda çok daha performanslı, verimli ve düşük güç tüketimli orta sınıf işlemcilerin piyasaya çıktığını görebiliriz.

Bu haberi, mobil uygulamamızı kullanarak indirip,istediğiniz zaman (çevrim dışı bile) okuyabilirsiniz:

İnce Satırlar

İnce Satırlar Liste Modu

Liste Modu Döşeme Modu

Döşeme Modu Sade Döşeme Modu

Sade Döşeme Modu Blog Modu

Blog Modu Hibrit Modu

Hibrit Modu

Bunlar zamanla Apple fiyatına araba verir